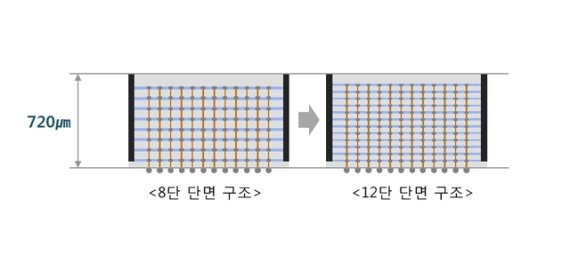

기존 8단 → 12단 적층 기술 개발 성공, 패키지 기술 한계 돌파

8단과 동일한 두께로 D램 칩 12단 적층, 시스템 설계 편의성 높여

초정밀 기술로 머리카락 굵기 1/20 수준 직경의 전기 통로 6만개 연결

고용량 고대역폭 메모리에 적용해 인공지능, HPC 분야 기술 선도

고객 수요에 맞춰 업계 최대 용량 24GB HBM(고대역폭 메모리) 양산 예정

삼성전자는 7일 업계 최초로 '12단 3D-TSV(3차원 실리콘 관통전극, 3D Through Silicon Via)' 기술을 개발했다고 밝혔다.

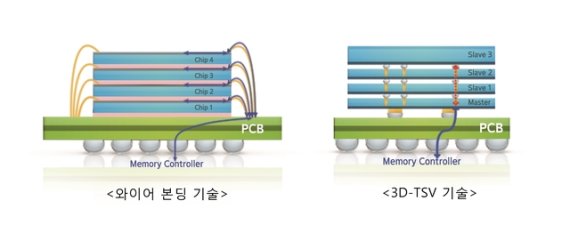

'12단 3D-TSV'는 기존 금선(와이어)을 이용해 칩을 연결하는 대신 반도체 칩 상단과 하단에 머리카락 굵기의 20분의 1수준인 수 마이크로미터 직경의 전자 이동 통로(TSV) 6만개를 만들어 오차 없이 연결하는 첨단 패키징 기술이다.

이 기술은 종이(100㎛)의 절반 이하 두께로 가공한 D램 칩 12개를 적층해 수직으로 연결하는 고도의 정밀성이 필요해 반도체 패키징 기술 중 가장 난이도가 높은 기술이다. '3D-TSV'는 기존 와이어 본딩(Wire Bonding) 기술보다 칩들 간 신호를 주고받는 시간이 짧아져 속도와 소비전력을 획기적으로 개선할 수 있는 점이 특징이다.

또 고대역폭 메모리에 '12단 3D-TSV' 기술을 적용해 기존 8단에서 12단으로 높임으로써 용량을 1.5배 증가시킬 수 있다.

삼성전자 DS부문 TSP총괄 백홍주 부사장은 "인공지능, 자율주행, HPC(High-Performance Computing) 등 다양한 응용처에서 고성능을 구현할 수 있는 최첨단 패키징 기술이 날로 중요해지고 있다"며 "기술의 한계를 극복한 혁신적인 '12단 3D-TSV 기술'로 반도체 패키징 분야에서도 초격차 기술 리더십을 이어가겠다"라고 말했다.

삼성전자는 고객 수요에 맞춰 '12단 3D-TSV' 기술을 적용한 고용량 HBM 제품을 적기에 공급해 프리미엄 반도체 시장을 지속 선도해 나갈 계획이다.

jmkim@newsis.com <저작권자ⓒ 공감언론 뉴시스통신사. 무단전재-재배포 금지.>

저작권자ⓒ 공감언론 뉴시스통신사. 무단전재-재배포 금지