인텔은 업계 최초로 실제 제품과 유사한 테스트 칩에 후면 전력 공급을 구현해 차세대 컴퓨팅 시대에 걸맞은 성능을 달성했다고 9일 밝혔다.

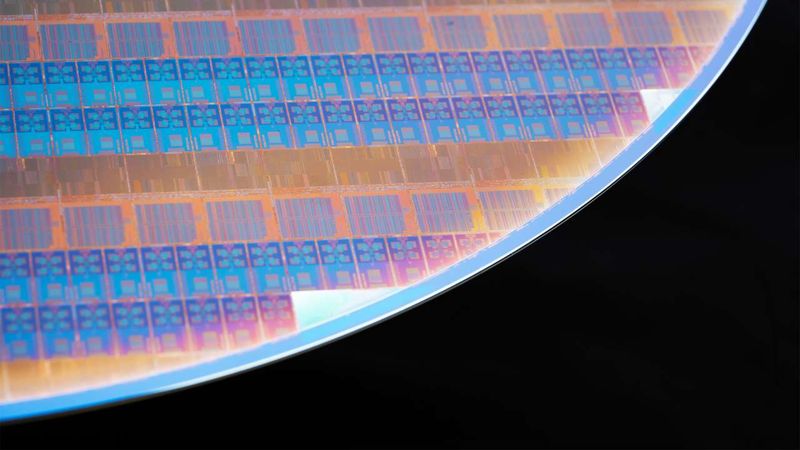

내년 상반기에 인텔 20A 공정 노드에 적용될 파워비아는 인텔의 후면 전력 공급 솔루션이다. 파워비아는 전력 라우팅을 웨이퍼의 후면으로 이동해 작업영역을 확장할 때 발생하는 상호 연결 병목 현상을 해결한다.

벤 셀 인텔 기술 개발 부문 부사장은 “파워비아는 인텔의 야심찬 ‘4년 내 5개 노드 달성’ 전략과 2030년까지 단일 패키징에 1조개의 트랜지스터 탑재 목표 달성에 주요한 이정표가 될 것”이라며 “시험 공정 노드와 후속 테스트 칩을 사용해 선도적인 공정 노드에 적용될 후면 전력 공급 위험성을 제거할 수 있었으며, 인텔은 후면 전력 공급 기술을 경쟁사 대비 한 발 먼저 시장에 선보일 수 있게 됐다”고 말했다.

인텔은 인텔 20A, 인텔 18A 공정 노드 기반 실리콘 구현 준비를 보장하기 위해 파워비아 개발과 트랜지스터 개발을 분리했다. 인텔은 파워비아를 인텔 20A의 리본펫과 통합하기 전 파워비아 내 버그를 제거하고 우수한 기능을 보장하기 위해 자체 내부 테스트 노드 상에서 파워비아에 대한 테스트를 진행했다.

해당 테스트를 통해 파워비아가 90% 이상의 셀 활용률, 트랜지스터 확장을 통해 칩 리소스를 매우 효율적으로 사용하며, 칩 설계자가 제품의 성능과 효율성을 향상할 수 있도록 지원한다는 것을 확인했다.

인텔은 오는 11일부터 16일까지 일본 교토에서 열리는 VLSI 심포지엄에서 해당 연구 결과를 발표할 예정이다.

인텔 20A와 인텔 18A는 파워비아 후면 전력 공급 기술 및 리본펫 GAA 기술을 모두 적용할 계획이다. 후면 전력 공급 기술은 트랜지스터에 전력을 공급하는 완전히 새로운 방식인 만큼 제품의 발열 관리와 버그 제거를 위한 설계에 있어 새로운 도전과제를 제시했다.

인텔은 이 문제를 해결하기 위해 리본펫 개발과 파워비아의 개발을 분리하여 인텔의 20A 및 18A 공정 노드 기반 실리콘에서 구현할 수 있도록 지원했다. 인텔 엔지니어들은 발열 문제를 방지하고자 완화 기술을 개발했다. 또 디버그 커뮤니티는 새로운 설계 구조에서 버그가 적절히 제거될 수 있도록 하는 새로운 기술을 개발했다. 그 결과 테스트 구현을 통해 견고한 수율 및 신뢰성 지표를 제공하는 동시에 새로운 리본펫 아키텍처에 합류하기 전 기술의 본질적인 가치를 입증해냈다.

더불어 이 테스트는 극자외선(EUV) 리소그래피로 구현된 설계 규칙을 활용하여 다이의 넓은 영역에서 90% 이상의 표준 셀 활용률 등의 결과를 도출했으며 셀 밀도를 높여 비용 절감 효과를 가져왔다. 또한 테스트 결과 30% 이상 플랫폼 전압 강하를 개선했고 6% 빠른 클럭 스피드를 보였다. 인텔은 로직 스케일링에서 예상되는 더 높은 전력 밀도에 맞춰 파워비아 테스트 칩에서 발열특성을 개선했다.

solidkjy@fnnews.com 구자윤 기자

※ 저작권자 ⓒ 파이낸셜뉴스, 무단전재-재배포 금지